Operator Library: Hardware Platform

The operator transfers image data from a Camera Link MEDIUM RGB configuration camera into VisualApplets. Three MEDIUM RGB configurations of the Camera Link standard are supported.

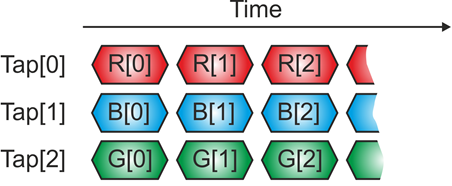

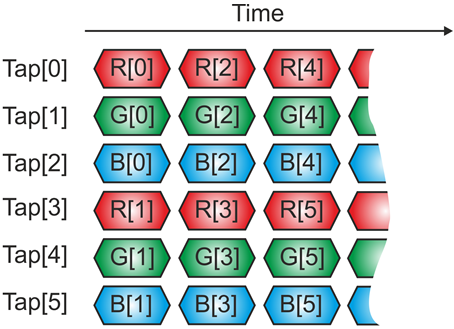

The following figures show the pixel mapping in these modes:

Tap3x10bit and Tap3x12bit:

Tap6x8bit:

The operator uses 2 ressources of type CameraPort exclusively. Thus, both ports of the frame grabber, port A (0) and port B (1), are occupied and cannot be used by other operators. The same ressource index can only be used once per applet.

| Available for Hardware Platforms |

|---|

| mE5 marathon VCLx |

| mE5 marathon VCL |

| LightBridge VCL |

| mE5 VD8-PoCL (ironman) |

| Link Parameter | Output Link O |

|---|---|

| Bit Width | [3,63] |

| Arithmetic | unsigned |

| Parallelism | Any, see parameter description |

| Kernel Columns | 1 |

| Kernel Rows | 1 |

| Img Protocol | {VALT_IMAGE2D,VALT_LINE1D} |

| Color Format | VAF_COLOR |

| Color Flavor | FL_RGB |

| Max. Img Width | Any |

| Max. Img Height | Any |

|

The bitwidth must be a multiple of 3 due to the RGB tuple. Parameter BitWidth can be set to a larger or smaller value than the actual bitwidth sent by the camera. If the parameter is set to a smaller value than the actual bitwidth sent by the camera, the least significant bits (LSB) of the pixel components are cut off. Only the most signicicant bits (MSB) per pixel component are transferred into VisualApplets. If the parameter is set to a bigger value than the actual bitwidth sent by the camera, the original pixel components are set on the MSB position of the outgoing pixel components. The LSBs are filled with zeros. In both cases, the relative brightness stays the same, i.e., white pixels remain withe and dark pixels remain dark. |

| DvalMode | |

|---|---|

| Type | dynamic write parameter |

| Default | DVAL_Enabled |

| Range | {DVAL_Enabled, DVAL_Disabled} |

|

The parameter specifies whether DVAL is used to mask valid pixels or if it is ignored. When DVAL is ignored, the valid pixels are selected according to LVAL and FVAL statuses. |

|

| FvalMode | |||||||

|---|---|---|---|---|---|---|---|

| Type | dynamic/static write parameter | ||||||

| Default | CameraLinkStandard | ||||||

| Range | {CameraLinkStandard, IgnoreFval} | ||||||

The intention of this parameter is to allow the usage of area scan an line scan cameras dynamically in the same applet. |

|||||||

| MediumMode | |

|---|---|

| Type | dynamic write parameter |

| Default | Tap3x10bit |

| Range | {Tap3x10bit, Tap3x12bit, Tap6x8bit} |

|

The parameter specifies the MEDIUM configuration mode. |

|

| CameraStatus | |

|---|---|

| Type | dynamic read parameter |

| Default | |

| Range |

LightBridge/marathon: [0;2^24-1] mE5 VD8 ironman: [0;2^8-1] |

|

Parameter CameraStatus depends on the frame grabber hardware you are programming for. Find below the descriptions first for marathon and Lightbridge, than for mE5 VD8-PoCL (ironman). marathon and Lightbridge: bit[0]: PCLK [0] available bit[1]: FVAL [0] current value bit[2]: LVAL [0] current value bit[3]: DVAL [0] current value bit[4-11]: reserved bit[12]: PCLK [1] available bit[13]: FVAL [1] current value bit[14]: LVAL [1] current value bit[15]: DVAL [1] current value bit[16-23]: reserved mE5 VD8-PoCL (ironman): bit[0]: PCLK [0] available bit[1]: FVAL [0] current value bit[2]: LVAL [0] current value bit[3]: DVAL [0] current value bit[4]: PCLK [1] available bit[5]: FVAL [1] current value bit[6]: LVAL [1] current value bit[7]: DVAL [1] current value |

|

| CameraLinkCoreReset | |

|---|---|

| Type | dynamic write parameter |

| Default | 0 |

| Range | [0; 1] |

|

Reserved for support issues. |

|

| PixelClockX | |

|---|---|

| Type | dynamic read parameter |

| Default | 0 |

| Range | [0; 85] MHz |

|

Pixel clock rate of camera channel X in MHz. |

|

| PixelClockY | |

|---|---|

| Type | dynamic read parameter |

| Default | 0 |

| Range | [0; 85] MHz |

|

Pixel clock rate of camera channel Y in MHz. |

|

| MinimalParallelism | |

|---|---|

| Type | static read parameter |

| Default | 2 |

| Range | [1; 1024] |

|

Minimal parallelism for the output link O to be able to transport the maximal bandwidth of the camera without losing data. This value depends on the currently selected design clock frequency. The higher the frequency the lower the parallelism value can become. |

|

![[Important]](../common/images/admon/important.png)

![[Note]](../common/images/admon/note.png)

![[Warning]](../common/images/admon/warning.png)

Prev

Prev